# Pole-to-ground Fault Analysis for HVDC Grid Based on Common- and Differential-mode Transformation

Zhen He, Sutdent Member, IEEE, Jiabing Hu, Senior Member, IEEE, Lei Lin, Member, IEEE, Yuanzhu Chang, Sutdent Member, IEEE, and Zhiyuan He, Member, IEEE

Abstract—Pole-to-ground (PTG) fault analysis is of vital importance for high-voltage direct current (HVDC) grid. However, many factors are not considered in the existing studies such as the asymmetrical property of PTG fault, the coupling issue between DC transmission lines and the complexity of the structure of DC grid. This paper presents a PTG fault analysis method, which is based on common- and differential-mode (CDM) transformation. Similar to the symmetrical component method in AC system, the transformation decomposes the HVDC grid into CDM networks, which is balanced and decoupled. Then, a transfer impedance is defined and calculated based on the impedance matrices of the CDM networks. With the transfer impedance, analytical expressions of fault characteristics that vary with space and time are obtained. The proposed PTG fault analysis method is applicable to arbitrary HVDC grid topologies, and provides a new perspective to understand the fault mechanism. Moreover, the analytical expressions offer theoretical guidance for PTG fault protection. The validity of the proposed PTG fault analysis method is verified in comparison with the simulation results in PSCAD/EMTDC.

Index Terms—High-voltage direct current (HVDC) grid, pole-to-ground (PTG) fault, common- and differential-mode(CDM) transformation, DC ciruit breaker (DCCB).

#### I. INTRODUCTION

OWADAYS, the modular multi-level converter based high-voltage direct current (MMC-HVDC) grid is attractive for renewable power integration [1] and global energy interconnection [2]-[4]. It can be configured by either symmetrical monopole or bipolar structure. Compared with the monopole structure, the symmetrical bipolar configuration shows advantages in bulk power transmission and DC fault-tolerate control [5]. Thus, the symmetrical bipolar based MMC-

Manuscript received: June 21, 2019; accepted: December 13, 2019. Date of CrossCheck: December 13, 2019. Date of online publication: April 9, 2020.

DOI: 10.35833/MPCE.2019.000419

HVDC grid, which has been recently adopted in the Zhangbei Project, China, becomes the research focus of this paper.

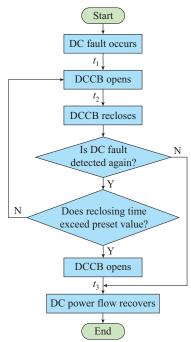

In HVDC grid, the pole-to-ground (PTG) fault is one of the most common DC-side faults. To protect the grid, lots of studies have been conducted, which can be summarized into two solutions [6]-[10]. The first solution is based on MMCs with the handling capability of DC fault. However, this solution needs to block the insulated gate bipolar transistors (IG-BTs) [6] or regulate the DC grid voltage to zero [7], [8], which will cause a temporary interruption of the active power transmission. The other solution relies on DC circuit breakers (DCCBs). The faulty DC lines can be selectively isolated with DCCBs, and the healthy DC parts can maintain continuous operation [9], [10]. On this basis, this solution is considered as a promising candidate for future large-scale HVDC grid [2]. Figure 1 shows the typical protection sequence of the DCCB-based solution under PTG fault, where  $t_1 \approx 5$  ms;  $t_2 \approx 150-500$  ms;  $t_3 \approx 100$  ms. The transient process is divided into three stages. Stage 1 is fault detecting and DCCB opening; Stage 2 is DC line deionizing; and Stage 3 is DC power flow recovering. Although Stage 1 is quite short (typically around 5 ms), fault transient voltage and current stresses are mainly concentrated in this stage. Thus, PTG fault analysis at Stage 1 can provide theoretical guidance for the selection of DC equipment and the parameter setting of protection relays, which is of vital importance for the HVDC grid.

Aiming at the fault analysis at Stage 1, the numerical and analytical calculations are two effective ways. From the aspect of numerical calculation, some electromagnetic transient (EMT) simulation work is documented in [11], [12], where accurate characteristics of PTG fault are presented. However, this analysis lacks profound understanding of the fault mechanism, and is quite time-consuming, especially for largescale HVDC grid. As for the analytical calculation, it can theoretically reveal the regularities underlying the fault characteristics. However, there also exist the following difficulties. Firstly, the PTG fault is a typical DC-side asymmetrical fault. The transient voltage and fault current in positive and negative poles are unbalanced. Secondly, with the mutual inductance between DC transmission lines, the fault transient processes of positive and negative poles are coupled. Thirdly, HVDC grid can be constructed with a variety of topolo-

This work was supported in part by National Key Research and Development Program of China (No. 2016YFB0900100).

This article is distributed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/).

Z. He, J. Hu (corresponding author), L. Lin, and Y. Chang are with State Key Laboratory of Advanced Electromagnetic Engineering and Technology, and School of Electrical and Electronic Engineering, Huazhong University of Science and Technology, Wuhan 430074, China (e-mail: hezhen\_hz@hust.edu.cn; j.hu@hust.edu.cn; linlei@hust.edu.cn; yzchang@hust.edu.cn).

Z. He is with Global Energy Interconnection Research Institute, State Grid, Beijing 100192, China.

gies including the radial type, the meshed type and a hybrid of the two types. Hence, it is hard to form a unified description that is suitable for arbitrary HVDC grid topologies.

*t*<sub>1</sub>: fault detecting & DCCB opening; *t*<sub>2</sub>: DC line deionizing *t*<sub>3</sub>: DC power flow recovering

Fig. 1. Typical protection sequence of DCCB-based solution under PTG fault.

The conducted studies focus on the above difficulties in analytical calculation at Stage 1. In line-commutated converter (LCC) based HVDC system, a common- and differential-mode (CDM) transformation is firstly proposed in [13] to overcome the imbalance and coupling issues. Based on that, fault transient overvoltage is analyzed in [13]. Characteristics of the initial values of traveling waves are investigated in [14]. And frequency responses of terminal current and voltage of the converter are presented in [15]. However, these studies merely focus on the two-terminal system, while the complexity of the structure of the DC grid is not considered. Reference [16] proposes a pole-to-pole (PTP) fault current calculation method for MMC-HVDC grid. However, this method is unsuitable for the PTG fault scenario because the attentions are not paid to the factor of mutual inductance.

In this paper, as a further attempt to analytically present the PTG fault characteristics at Stage 1 of the protection sequence, two contributions are made: ① considering the concept of CDM transformation and the complexity of DC grid structure, a generic PTG fault analysis method is proposed, which is suitable for arbitrary HVDC grid topologies; ② based on the proposed method, analytical expressions of the fault characteristics that vary with space and time are derived, which is expected to be applied to the selection of DC protection equipment and parameter setting of protection relays.

The rest of this paper is organized as follows. The basic principle of CDM transformation is introduced in Section II.

Based on that, a PTG fault analysis method is proposed in Section III and Section IV gives the analytical expressions of PTG fault characteristics. Then, a simulation study based on Zhangbei Project in China is conducted in Section V for verification. Section VI briefly discusses the practical application of the proposed method of PTG fault analysis. Finally, Section VII draws the conclusions.

### II. BASIC PRINCIPLE OF CDM TRANSFORMATION

In LCC-HVDC, the DC-side PTG fault will also cause the imbalance and coupling issues [13]-[15]. The CDM transformation proposed in [13] is an effective tool for analyzing the asymmetrical phenomenon, which shows a similar function as the symmetrical component method in AC system. In this section, the basic principle of CDM transformation is briefly reviewed for a better understanding of the proposed analysis method. Taking DC current as an example, the transformation can be expressed as:

$$\begin{bmatrix} i^{\Sigma} \\ i^{\Delta} \end{bmatrix} = \frac{1}{2} \begin{bmatrix} 1 & 1 \\ 1 & -1 \end{bmatrix} \begin{bmatrix} i_p \\ i_n \end{bmatrix} \tag{1}$$

where the subscripts p and n are the positive and negative pole components, respectively; and the superscripts  $\Sigma$  and  $\Delta$  are the CDM components. With the transformation, a pair of unbalanced positive and negative pole currents can be decomposed into two couples of balanced CDM components. This property is employed in the following sections to analyze the PTG fault.

## III. CDM Transformation Based PTG Fault Analysis Method

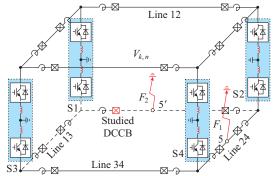

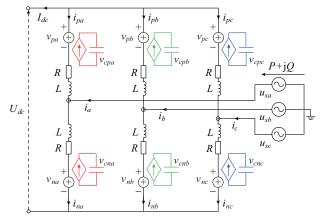

In this section, based on the CDM transformation, a PTG fault analysis method is proposed. The main idea contains two aspects. Firstly, to address the imbalance and coupling issues, the HVDC grid is transferred into CDM networks. Secondly, from the perspective of CDM components, a transfer impedance based analysis is performed. Thus the analytical expression of the PTG fault point current is obtained. Figure 2(a) shows an arbitrary HVDC grid. It contains n nodes and p branches. The nodes consist of p active nodes (with MMC connected) and p passive nodes (without MMC connected). Without the loss of generality, a PTG fault is assumed to occur at the negative pole of DC line. The fault point is defined as the  $(n+1)^{th}$  node.

## A. CDM Transformation of HVDC Grid

#### 1) DC Transmission Lines

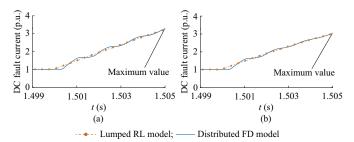

The DC transmission line can be modeled as the distributed frequency-dependent (FD) model [14]-[16] or the lumped RL model [17], [18]. Figure 3 shows a comparison of DC fault current when the lumped RL model and the distributed FD model are adopted. Figure 3(a) is in the scenario of low-fault resistance (0.01  $\Omega$ ) while Fig. 3(b) is in the scenario of high-fault resistance (15  $\Omega$ ). It is found that the fault current employing the lumped RL model is the average approximation of the fault current employing distributed FD model. Moreover, although transient oscillation is observed in the scenario adopting FD model, it decays with time. And the at-

tenuation of the oscillation trends to be more obvious in the scenario of large fault resistance. Based on the aforementioned average approximation and the attenuation effect, the transient oscillation has little impact on the calculation of the maximum fault current value. Thus, the lumped RL model, previously used in [17], [18], is adopted in this paper for the current stress estimation.

Fig. 2. Symmetrical bipolar based MMC-HVDC grid. (a) Grid Topology. (b) DC transmission line. (c) MMC station. (d) Fault boundary condition.

Fig. 3. DC fault current comparison under different fault resistance scenarios. (a) Fault resistance is 0.01  $\Omega$ . (b) Fault resistance is 15  $\Omega$ .

Figure 2(b) shows the RL model of DC transmission line, where nodes j and k are the terminals of the transmission line; G represents the ground;  $V_j$  and  $V_k$  are the voltages (with respect to ground) of nodes j and k, respectively;  $i_{jk}$  is the branch current;  $L_{jk,line}$  and  $M_{jk,line}$  are the self and mutual inductances of branch jk, respectively;  $R_{ik,line}$  is the line resis-

tance; and  $L_{jk,dc}$  and  $L_{kj,dc}$  are the DC reactors close to node j and node k, respectively. Based on Fig. 2(b), the KVL equation is written as:

$$\begin{bmatrix}

V_{j,p} - V_{k,p} \\

V_{j,n} - V_{k,n}

\end{bmatrix} = R_{jk,line} \begin{bmatrix} i_{jk,p} \\ i_{jk,n} \end{bmatrix} + \\

\begin{bmatrix}

L_{jk,dc} + L_{kj,dc} + L_{jk,line} & M_{jk,line} \\

M_{jk,line} & L_{jk,dc} + L_{kj,dc} + L_{jk,line} \end{bmatrix} \frac{\mathbf{d}}{\mathbf{d}t} \begin{bmatrix} i_{jk,p} \\ i_{jk,n} \end{bmatrix} \tag{2}$$

In (2), the non-diagonal elements of the coefficient matrix are not zero, which implies the coupling of positive and negative poles. Thus, the PTG fault characteristics cannot be solved independently from positive or negative poles. To address the problem, the transformation in (1) is applied, and (2) is transferred to (3):

$$\begin{bmatrix}

V_{j}^{\Sigma} - V_{k}^{\Sigma} \\

V_{j}^{\Delta} - V_{k}^{\Delta}

\end{bmatrix} = R_{jk,line} \begin{bmatrix} i_{jk}^{\Sigma} \\ i_{jk}^{\Delta} \end{bmatrix} + \\

\begin{bmatrix}

L_{jk,dc} + L_{kj,dc} + L_{jk,line} & 0 \\

0 & L_{jk,dc} + L_{kj,dc} + L_{jk,line}^{\Delta} \end{bmatrix} \frac{\mathrm{d}}{\mathrm{d}t} \begin{bmatrix} i_{jk}^{\Sigma} \\ i_{jk}^{\Delta} \end{bmatrix} \tag{3}$$

$$L_{jk,line}^{\Sigma} = L_{jk,line} + M_{jk,line} \\

L_{jk,line}^{\Delta} = L_{jk,line} - M_{jk,line}$$

It can be observed that (3) is under the perspective of CDM components, where the coupling terms in the coefficient matrix have disappeared.

### 2) MMC Stations

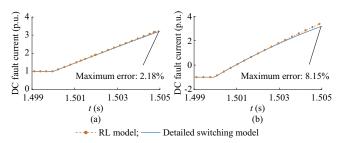

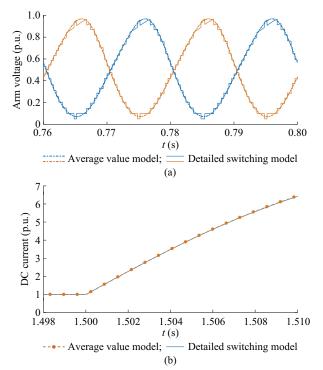

As indicated in Section I, this study focuses on Stage 1 of the PTG fault protection sequence (about 5 ms). At this stage, the MMC station is still in the normal operation mode. Some fault transient controls such as the blocking and fault ride through control, do not need to be considered. In [19], the RLC model is employed to calculate the fault characteristics of MMC. However, further elaboration presents that the voltage variation of DC-side equivalent capacitor at this stage is within 0.1 p.u., as listed in the Appendix A. Hence, the RLC model can be further equivalent to an RL model, as shown in Fig. 2(c), where  $V_{dci}$  is the rated DC voltage;  $i_i$  is the DC current; and  $R_i$  and  $L_i$  are the DC-side equivalent resistance and inductance, respectively. The subscript i represents the  $i^{th}$  (i = 1, 2, ..., m) MMC station. Figure 4 shows the DC fault current comparison between RL model and detailed switching model in different operation modes. The comparison is under the precondition that the MMC is not blocked (arm currents are limited to 1.7 p.u.). It is found that during the initial 5 ms, the maximum error between the two modes is within 10%. Thus, it is accurate enough to estimate the fault current of MMC by RL model.

Fig. 4. DC fault current comparison between RL model and detailed switching model. (a) Rectifier operation mode. (b) Inverter operation mode.

Based on Fig. 2(c), the KVL equation can be written as:

$$\begin{bmatrix} V_{i,p} \\ V_{i,n} \end{bmatrix} = \begin{bmatrix} V_{dci} \\ -V_{dci} \end{bmatrix} - L_i \frac{d}{dt} \begin{bmatrix} i_{i,p} \\ i_{i,n} \end{bmatrix} - R_i \begin{bmatrix} i_{i,p} \\ i_{i,n} \end{bmatrix}$$

(4)

With CDM transformation, (4) is transferred as:

$$\begin{bmatrix} V_{i}^{\Sigma} \\ V_{i}^{\Delta} \end{bmatrix} = \begin{bmatrix} 0 \\ V_{dci}^{\Delta} \end{bmatrix} - L_{i} \frac{d}{dt} \begin{bmatrix} i_{i}^{\Sigma} \\ i_{i}^{\Delta} \end{bmatrix} - R_{i} \begin{bmatrix} i_{i}^{\Sigma} \\ i_{i}^{\Delta} \end{bmatrix}$$

(5)

## 3) Fault Boundary Condition

When a negative PTG fault occurs, the fault boundary condition is depicted in Fig. 2(d). It can be expressed as:

$$\begin{cases} i_{(n+1),p} = 0 \\ V_{(n+1),n} = R_f i_{(n+1),n} \end{cases}$$

(6)

where  $R_f$  is the fault resistance. Transforming (6) into its CDM components, we can obtain:

$$\begin{cases} i_{(n+1)}^{\Sigma} + i_{(n+1)}^{\Delta} = 0\\ V_{(n+1)}^{\Sigma} - V_{(n+1)}^{\Delta} = R_{f} \left( i_{(n+1)}^{\Sigma} - i_{(n+1)}^{\Delta} \right) \end{cases}$$

(7

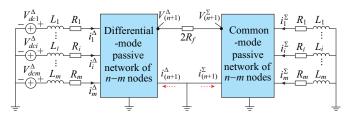

Then, combining (3), (5) and (7), the transformed DC transmission lines, MMC stations and PTG fault boundary condition constitute the CDM networks, as shown in Fig. 5. At this point, from the perspective of CDM components, the imbalance and coupling issues do not exist, which is of benefit to the following analysis of PTG fault.

Fig. 5. CDM networks.

## B. Impedance Matrix Deduction of CDM Networks

In this part, the impedance matrices of CDM networks are derived. Firstly, the admittance of DC lines and MMC stations are expressed in the form of 1/(Ls+R), where s is the Laplace operator. Then, based on the structure of HVDC grid, the admittance matrices of CDM networks are written as  $Y^{\Sigma}$  and  $Y^{\Delta}$ . By inverting  $Y^{\Sigma}$  and  $Y^{\Delta}$ , the impedance matrices can be obtained.

$$\mathbf{Z}^{\Sigma} = (\mathbf{Y}^{\Sigma})^{-1} = \begin{bmatrix} Z_{11}^{\Sigma} & Z_{12}^{\Sigma} & \cdots & Z_{1(n+1)}^{\Sigma} \\ Z_{21}^{\Sigma} & Z_{22}^{\Sigma} & \cdots & Z_{2(n+1)}^{\Sigma} \\ \vdots & \vdots & & \vdots \\ Z_{(n+1)1}^{\Sigma} & Z_{(n+1)2}^{\Sigma} & \cdots & Z_{(n+1)(n+1)}^{\Sigma} \end{bmatrix}$$

(8)

$$\mathbf{Z}^{\Delta} = (\mathbf{Y}^{\Delta})^{-1} = \begin{bmatrix} Z_{11}^{\Delta} & Z_{12}^{\Delta} & \cdots & Z_{1(n+1)}^{\Delta} \\ Z_{21}^{\Delta} & Z_{22}^{\Delta} & \cdots & Z_{2(n+1)}^{\Delta} \\ \vdots & \vdots & & \vdots \\ Z_{(n+1)1}^{\Delta} & Z_{(n+1)2}^{\Delta} & \cdots & Z_{(n+1)(n+1)}^{\Delta} \end{bmatrix}$$

(9)

However, it should be noted that the Laplace operator s in  $Y^{\Sigma}$  and  $Y^{\Delta}$  cannot be substituted by  $j\omega$  directly since Stage 1 of the PTG fault protection sequence is a transient process. As a result, the inverting process will be very complicated if

the grid resistance is considered.

Fortunately, the voltage drop on the grid resistors, including the DC-side equivalent resistor of the converter and the DC line resistor, is much smaller than those on the inductors during Stage 1. Thus, the grid resistors are neglected in this paper, and the inverting process of admittance matrices is largely simplified.

## C. Transfer Impedance Based PTG Fault Analysis

According to the superposition theorem, the voltage of  $(n+1)^{th}$  node can be expressed as the sum of the voltage generated by each fault excitation source. Thus, based on Fig. 5, the voltage of the fault point is written as:

$$V_{(n+1)}^{\Delta} = \sum_{i=1}^{m} \frac{V_{dci}^{\Delta}}{z_{i}^{\Delta}} Z_{i(n+1)}^{\Delta} - Z_{(n+1)(n+1)}^{\Delta} \dot{t}_{(n+1)}^{\Delta}$$

(10)

where  $z_i$  is the DC-side equivalent impedance of the  $i^{\text{th}}$  MMC station. Meanwhile, the relation between  $V_{(n+1)}^{\Delta}$  and  $i_{(n+1)}^{\Delta}$  can also be expressed as:

$$i_{(n+1)}^{\Delta} = -i_{(n+1)}^{\Sigma} = \frac{V_{(n+1)}^{\Delta}}{2R_f + Z_{(n+1)(n+1)}^{\Sigma}}$$

(11)

Substituting (10) into (11), we can obtain:

$$i_{(n+1)}^{\Delta} = -i_{(n+1)}^{\Sigma} = \frac{\sum_{i=1}^{m} V_{dci}^{\Delta} Z_{i(n+1)}^{\Delta} / Z_{i}^{\Delta}}{2R_{f} + Z_{(n+1)(n+1)}^{\Sigma} + Z_{(n+1)(n+1)}^{\Delta}}$$

(12)

Then, the transfer impedance  $z_{is,i}$  is defined as:

$$z_{is,i} = z_i^{\Delta} \left( 2R_f + Z_{(n+1)(n+1)}^{\Sigma} + Z_{(n+1)(n+1)}^{\Delta} \right) / Z_{i(n+1)}^{\Delta}$$

(13)

Hence, (12) is simplified as:

$$i_{(n+1)}^{\Delta} = -i_{(n+1)}^{\Sigma} = \sum_{i=1}^{m} V_{dci}^{\Delta} / z_{js,i}$$

(14)

The value of  $z_{js,i}$  is determined by the structure and parameters of the HVDC grid, which can be calculated by the deduced impedance matrices. From (14), it is seen that the analytical expression of fault current can be acquired as long as the transfer impedance is calculated. But (14) is expressed in frequency domain. To obtain the analytical expression in time domain, the calculated transfer impedance  $z_{js,i}$  is rewritten in form of  $(R_{js,i}+sL_{js,i})$ , where  $R_{js,i}$  and  $L_{js,i}$  are the equivalent resistance and inductance of  $z_{js,i}$ , respectively. Thus, the PTG fault current in time domain is deduced as:

$$i_{(n+1)}^{\Delta} = -i_{(n+1)}^{\Sigma} = \sum_{i=1}^{m} \frac{V_{dci}}{R_{js,i}} \left( 1 - e^{-\left( R_{js,i} / L_{js,i} \right) t} \right)$$

(15)

## IV. ANALYTICAL EXPRESSIONS OF PTG FAULT TRANSIENT VOLTAGE AND CURRENT

Section III proposes a CDM transformation based PTG fault analysis method, where the analytical expression of fault point current that varies with time is obtained. In this section, further analysis of the fault characteristics that vary with space is presented.

## A. Distribution of Fault Transient Voltage in HVDC Grid

In this part, the distribution of fault transient voltage along arbitrary branch is deduced. As shown in Fig. 6, x is

(20)

defined as the ratio between the distance from the studied point to the branch node with the largest index and the total branch length. The transient voltage of any node in the CDM networks can be derived as the sum of its initial value and the voltage increment which is generated by the fault current:

$$V_{i}^{\Sigma} = V_{i,0}^{\Sigma} - i_{(n+1)}^{\Sigma} Z_{i(n+1)}^{\Sigma} \tag{16}$$

$$V_{i}^{\Delta} = V_{i,0}^{\Delta} - i_{(n+1)}^{\Delta} Z_{i(n+1)}^{\Delta} \tag{17}$$

where the subscript 0 means the initial value. It can be obtained with the steady-state power flow calculation method [20]. Thus, the distribution of fault transient voltages along branch *jk* is written as:

$$V_{x}^{\Delta} = \frac{L_{jk,dc} + (1-x)L_{jk,line}^{\Delta}}{L_{ik}^{\Delta}}V_{k}^{\Delta} + \frac{L_{kj,dc} + xL_{jk,line}^{\Delta}}{L_{ik}^{\Delta}}V_{j}^{\Delta}$$

(18)

$$V_{x}^{\Sigma} = \frac{L_{jk,dc} + (1 - x)L_{jk,line}^{\Sigma}}{L_{ik}^{\Sigma}} V_{k}^{\Sigma} + \frac{L_{kj,dc} + xL_{jk,line}^{\Sigma}}{L_{ik}^{\Sigma}} V_{j}^{\Sigma}$$

(19)

where  $L_{jk}$  is the inductance of branch jk with the consideration of DC reactors, satisfying  $L_{jk}^{\Sigma} = L_{jk,dc} + L_{kj,dc} + L_{jk,line}^{\Sigma}$  and  $L_{jk}^{\Delta} = L_{jk,dc} + L_{kj,dc} + L_{jk,line}^{\Delta}$ .

Then, with inverse CDM transformation, the transient voltages in positive and negative poles are obtained as:

$$\begin{cases} V_{x,p} = V_x^{\Sigma} + V_x^{\Delta} \\ V_{x,n} = V_x^{\Sigma} - V_x^{\Delta} \end{cases}$$

$$\downarrow L_{jk,dk} \qquad \downarrow L_{jk,line} \qquad \downarrow L_{jk,line} \qquad \downarrow L_{jk,line} \qquad \downarrow L_{jk,dk} \qquad \downarrow L_{kj,dk} \qquad$$

Fig. 6. Distribution of fault transient voltage along branch jk. (a) Commonmode branch. (b) Differential-mode branch.

(b)

### B. Distribution of Fault Current in HVDC Grid

In this part, the arbitrary branch current in the HVDC grid is deduced. Based on (18) and (19), any branch current in CDM networks can be acquired. Take branch jk as an example, we can obtain:

$$i_{jk}^{\Sigma} = \frac{V_{j}^{\Sigma} - V_{k}^{\Sigma}}{z_{jk}^{\Sigma}} = i_{jk,0}^{\Sigma} - i_{(n+1)}^{\Sigma} \frac{Z_{j(n+1)}^{\Sigma} - Z_{k(n+1)}^{\Sigma}}{z_{jk}^{\Sigma}}$$

(21)

$$i_{jk}^{\Delta} = \frac{V_j^{\Delta} - V_k^{\Delta}}{z_{jk}^{\Delta}} = i_{jk,0}^{\Delta} - i_{(n+1)}^{\Delta} \frac{Z_{j(n+1)}^{\Delta} - Z_{k(n+1)}^{\Delta}}{z_{jk}^{\Delta}}$$

(22)

where  $z_{jk}$  is the impedance of branch jk, satisfying  $z_{jk}$ = $sL_{jk}$ . For branches that connect active node i (i=1, 2, ..., m) and the ground, (21) and (22) are also applicable and can be rewritten as:

$$i_i^{\Sigma} = \frac{-V_i^{\Sigma}}{z_i^{\Sigma}} = i_{i,0}^{\Sigma} + i_{(n+1)}^{\Sigma} \frac{Z_{i(n+1)}^{\Sigma}}{z_i^{\Sigma}}$$

(23)

$$i_{i}^{\Delta} = \frac{-V_{i}^{\Delta}}{z_{i}^{\Delta}} = i_{i,0}^{\Delta} + i_{(n+1)}^{\Delta} \frac{Z_{i(n+1)}^{\Delta}}{z_{i}^{\Delta}}$$

(24)

Thus, with inverse CDM transformation, the fault currents in positive and negative poles are obtained:

$$\begin{cases}

i_{jk,p} = i_{jk}^{\Sigma} + i_{jk}^{\Delta} \\

i_{jk,n} = i_{ik}^{\Sigma} - i_{ik}^{\Delta}

\end{cases}$$

(25)

$$\begin{cases} i_{i,p} = i_i^{\Sigma} + i_i^{\Delta} \\ i_{i,n} = i_i^{\Sigma} - i_i^{\Delta} \end{cases}$$

(26)

Although (25) and (26) do not involve the space variable x, they are the fault currents at different DC lines in the CDM networks, which still contain the space information.

#### V. COMPARATIVE STUDY WITH SIMULATION

To verify the validity of the proposed fault analysis method, a symmetrical bipolar four-terminal MMC-HVDC grid is built in PSCAD/EMTDC. It is based on Zhangbei Project in China, and its configuration is shown in Fig. 7. The MMC station employs the average value model, which can reduce the computational efforts with satisfactory accuracy [21]. The configuration of the average value model is depicted in Appendix B, and parameters of the MMC stations are listed in Table I.

→ DC line reactor (150 mH); → Neutral line reactor (300 mH)

- DCCB; - MMC Station

Fig. 7. Symmetrical bipolar based four-terminal MMC-HVDC grid.

TABLE I PARAMETERS OF MMC STATIONS

| Parameter                   | Value |       |      |       |

|-----------------------------|-------|-------|------|-------|

|                             | S1    | S2    | S3   | S4    |

| Rated DC voltage (kV)       | ±500  | ±500  | ±500 | ±500  |

| Rated AC voltage (kV)       | 260   | 260   | 260  | 260   |

| Rated active power (MW)     | 1500  | -1500 | 3000 | -3000 |

| Rated reactive power (Mvar) | -300  | -300  | -600 | -600  |

| Number of SMs               | 218   | 218   | 218  | 218   |

| *SM capacitance (mF)        | 8     | 8     | 15   | 15    |

| *Arm inductance (mH)        | 100   | 100   | 50   | 50    |

| *Arm resistance (Ω)         | 1.32  | 1.32  | 0.66 | 0.66  |

|                             |       |       |      |       |

Note: \* indicates that considering the symmetry, parameters of positive MMC are listed.

The DC transmission line adopts the distributed FD model for precisely reflecting the EMT process [22]. The parameters of RL model based DC line are those of the FD model at 200 Hz [14]. The resistance per unit length is 0.0028  $\Omega$ / km; the self-inductance per unit length is 1.924 mH/km; and the mutual inductance per unit length is 0.996 mH/km.

As shown in Fig. 7, two negative PTG faults  $(F_1 \text{ and } F_2)$ are assumed to occur in the middle of Line 24 and Line 12 at 1.5 s, respectively. The node numbers of  $F_1$  and  $F_2$  are 5 and 5', respectively. The fault resistance of  $F_1$  is set to 15  $\Omega$ , while that of  $F_2$  is set to 0.01  $\Omega$ . Meanwhile, considering the interruption time of DCCB, the duration of Stage 1 is set to be 5 ms. During PTG fault, the DCCBs in HVDC grid are assumed not to open, which aims to see the correctness and accuracy of the PTG fault analysis at Stage 1.

## A. Validation of MMC Average-value Model

A comparative study between the detailed switching model of MMC and the average value model is performed to analyze their steady state and fault transient performance. Both models adopt the parameters listed in Appendix B, Table B1. The equivalent capacitance of each arm in average value model is C/N. Figure 8 shows the comparison results.

Fig. 8. Comparison between detailed switching model and average value model. (a) Arm voltage of phase A at steady state. (b) DC current during DC fault.

Figure 8(a) is the arm voltage of phase A in steady state. Compared with the detailed switching model, the average value model neglects the nearest level modulation (NLM) process. Without considering the NLM process, the performance of average value model matches well with that of the detailed switching model. Actually, if the number of SMs increases to several hundred (e.g., 200), the mismatch caused by the NLM process will be largely decreased. Figure 8(b) is the DC current during DC fault. The fault characteristics

of the average value model still match well with that of the detailed switching model. Combining Fig. 8(a) and (b), it can be concluded that the average equivalence is accurate and adequate for the reason on steady-state and fault transient characteristics.

## B. Comparison Between Analytical PTG Fault Characteristics and Simulation Results

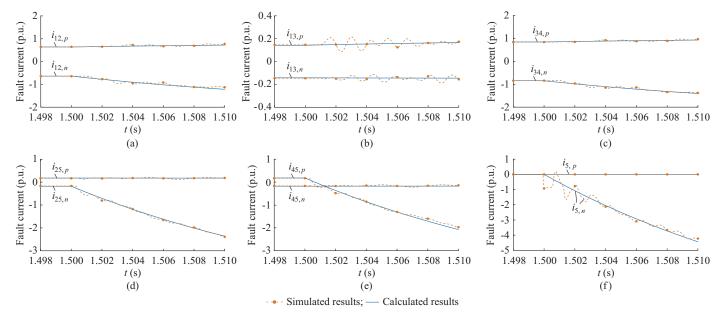

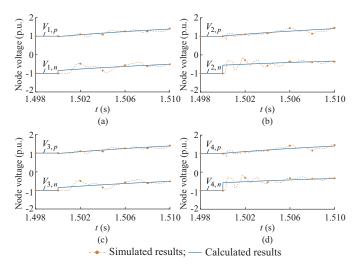

The fault  $F_1$  is taken as an example. According to the proposed analysis method, the HVDC grid is transformed into Fig. 9, which consists of fault boundary condition and CDM networks. Neglecting the resistance, the impedance matrices are written as:

$$Z^{\Sigma} = s \begin{bmatrix} 0.20 & 0.05 & 0.08 & 0.03 & 0.04 \\ 0.05 & 0.22 & 0.03 & 0.06 & 0.14 \\ 0.08 & 0.03 & 0.19 & 0.05 & 0.04 \\ 0.03 & 0.06 & 0.05 & 0.21 & 0.13 \\ 0.04 & 0.14 & 0.04 & 0.13 & 0.35 \end{bmatrix}$$

$$Z^{\Delta} = s \begin{bmatrix} 0.18 & 0.06 & 0.07 & 0.04 & 0.05 \\ 0.07 & 0.18 & 0.04 & 0.07 & 0.13 \\ 0.07 & 0.04 & 0.17 & 0.06 & 0.05 \\ 0.04 & 0.07 & 0.06 & 0.18 & 0.12 \\ 0.05 & 0.13 & 0.05 & 0.12 & 0.24 \end{bmatrix}$$

$$V_{\Delta}^{\Sigma}$$

$$V_{\Delta}^{\Sigma$$

Differential-mode

network

condition Transformed CDM networks and fault boundary condition.

Fault boundary

Common - mode

Substituting the impedance matrices into (13), the transfer acquired as  $z_{js,1} \approx (210.12 + 4.13s) \Omega$ , impedances are  $z_{js,2} \approx (198.61 + 3.90s) \Omega$ ,  $z_{js,3} \approx (87.73 + 1.72s) \Omega$ ,  $z_{js,4} \approx (82.36 + 1.89s) \Omega$ 1.62s)  $\Omega$ . Then, based on (15)-(19) and (21)-(24), the CDM components of PTG fault transient voltage and current are deduced. Furthermore, with inverse CDM transformation, the fault characteristics in positive and negative poles are obtained, and the validity is verified by comparison with the simulation results.

Figures 10 and 11 show the comparison of the calculated and simulated fault current and node voltage, respectively. Both simulation and calculation results are presented in per unit values, where the current base is 3 kA and the voltage base is 500 kV. In Figs. 10 and 11, transient oscillation components and their attenuation effect can be observed in the simulated fault current and voltage. The oscillation phenomena is due to the interaction between DC line inductance and stray capacitance, and the attenuation effect is determined by the DC resistance. Without consideration of the transient oscillations, the calculated curves match highly with the simulated results at Stage 1 of the protection sequence (5 ms), which verifies the validity of the proposed fault analysis method.

Fig. 10. Comparison of calculated fault current for fault  $F_1$  with simulated current. (a) Branch 12. (b) Branch 13. (c) Branch 34. (d) Branch 25. (e) Branch 45. (f) Fault point.

Fig. 11. Comparison of the calculated node voltage for fault  $F_1$  with simulated results. (a) Node 1. (b) Node 2. (c) Node 3. (d) Node 4.

It should be pointed out that the transient oscillation components are associated with the frequency-dependent parameters of DC line [15], [22]. Analytical description of the oscillations is quite complicated and difficult. Although this paper does not take the oscillations into consideration, the proposed analysis can still be applied to the selection of DC equipment, which will be presented in the following section.

## C. Influence of DC Inductance on Calculation Accuracy

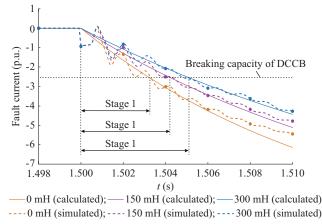

The influence of DC inductance on the calculation accuracy is investigated. Take the fault  $F_1$  as an example, and the fault point current  $i_{5,n}$  is observed. Figure 12 shows the comparison of the calculated and simulated fault current with different neutral line reactors. It can be found that the calculation accuracy decreases with the reduction of DC line inductance (neutral line reactor). This is because the fault current rises more rapidly with a reduction of DC line inductance.

Therefore, the variation of sub-module capacitor voltage exceeds 0.1 p.u., which results in an invalid DC-side equivalence of MMC station. However, the breaking capacity of DCCB is limited. As shown by the black dashed line in Fig. 12, with the reduction of DC line inductance, the duration time of Stage 1 is shortened. At Stage 1 of each scenario, the calculated results still match well with the simulation. Thus, it can be concluded that the proposed PTG fault analysis method has a satisfactory calculation accuracy with different DC line inductances.

Fig. 12. Comparison of calculated and simulated fault current with different neutral line reactors.

## D. Application of Proposed Fault Analysis Method

As mentioned above, the proposed fault analysis method can be used to select the DC protection equipment such as DCCBs. In this section, it is illustrated by a case.

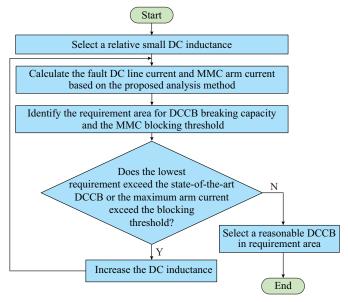

Take the selection of DCCB at the negative pole of line 12, which is marked with red in Fig. 7, as an example. The selection procedure is presented in Fig. 13. Firstly, considering rapid dynamic performance, a relatively small DC induc-

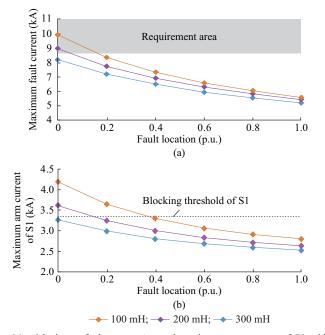

tance (the neutral line reactor equals to 100 mH in this case) is selected. Since the DCCB should be able to isolate any negative PTG fault on line 12 within limited duration of Stage 1 (5 ms) and guarantee the continuous operation of the MMC stations, the maximum fault current  $i_{15,n}$  and the maximum arm current of S1 with different fault locations on line 12 are calculated based on the proposed analysis method, respectively. Calculation results are shown in Fig. 14, where the abscissa axis means the ratio of the distance between the fault location and node 1 to the total length of line 12.

Fig. 13. Flowchart of DCCB selection.

Fig. 14. Maximum fault current  $i_{15,n}$  and maximum arm current of S1 with different fault locations and neutral line reactors. (a) Maximum fault current  $i_{15,n}$  (b) Maximum arm current of S1.

As shown in Fig. 14(a), based on the maximum value of  $i_{15,n}$  and considering the transient oscillations, the require-

ment area for DCCB breaking capacity, which is marked with shadow in Fig. 14(a), can be identified. Meanwhile, the blocking threshold of S1 is depicted as the dashed line in Fig. 14(b). If the lowest requirement for DCCB exceeds the state-of-the-art DCCB or the maximum arm current exceeds the blocking threshold, the DC inductance should be increased to lower the requirement, which is shown as the purple and blue lines in Fig. 14(a) and (b). The corresponding DCCB can be selected until the available DCCB can satisfy the lowest requirement and does not cause the blocking of S1.

#### VI. DISCUSSION

In Section V, the proposed analysis method is applied to the selection of DCCB. In this section, other practical applications are discussed.

## A. Optimal Design of DC Inductance

Both the dynamic performance and fault protection requirements need to be considered for the design of DC inductance [23]. In Section V, the fault current calculation accuracy with different DC inductances has been verified. Thus, the maximum fault current with different DC inductances can be calculated. In the scenarios with limited breaking capacity of DCCB, the calculated maximum fault current can be used to identify the limited value of DC inductance [24], which is important for the optimal design of DC inductance.

## B. Parameter Setting of DC Terminal Protection Relays

It should be pointed out that the proposed analysis method is not suitable for the parameter setting of DC line protection relays, since the transient oscillations are not considered. However, it is applicable for the setting of DC terminal protection relays.

The DC terminal protection relays of MMC are mainly based on the instantaneous values of arm current and DC terminal voltage. Although the transient oscillations are not considered in the proposed analysis method, the transient oscillations would be filtered out by the DC line reactors and DC-side shunt filters [22]. Thus, the proposed fault analysis method can still be used to calculate the instantaneous values of MMC arm current and DC terminal voltage. Based on that, parameters of DC terminal protection relays can be properly set.

## VII. CONCLUSION

This paper investigates the PTG fault characteristics in a symmetrical bipolar based MMC-HVDC grid. A CDM transformation based PTG fault analysis method is proposed. Compared with the existing work, the factors including the asymmetrical property of PTG fault, the coupling between DC transmission lines and the complexity of the structure of DC grid are all considered. Based on the analysis method, analytical expressions of the PTG fault characteristics that vary with space and time are obtained. Simulation results show that the calculated fault characteristics are accurate and can be applied to the selection of DC protection equipment.

#### APPENDIX A

The time constant of SM capacitor  $\tau$  is defined as the ratio of the energy stored in the sub-modules (SMs) to the rated active power:

$$\tau = \frac{C_{eq}V_{dc}^2}{2V_{dc}I_{dc}} = \frac{C_{eq}V_{dc}}{2I_{dc}}$$

(A1)

where  $C_{eq}$  is the DC-side equivalent capacitance. The typical value of  $\tau$  is around 50 ms. At Stage 1 of the fault protection sequence, the DC current variation can be approximately considered to be linear. Thus, the voltage variation of DC equivalent capacitor is expressed as:

$$\Delta V_{dc} = \frac{1}{C_{ea}} \int_{0}^{T_{stage1}} \Delta I_{dc} dt = \frac{1}{2C_{ea}} \Delta I_{dc} T_{stage1}$$

(A2)

where  $\Delta V_{dc}$  is the voltage variation;  $\Delta I_{dc}$  is the DC current increment; and  $T_{stage1}$  is the time durations of Stage 1 (typically around 5 ms). The following are the deviations of the maximum voltage variation of MMC  $\Delta V_{dc}$  in rectifier and inverter operation modes, respectively.

## 1) Rectifier Operation Mode

Considering only the fundamental DC frequency components, the maximum arm current of MMC during the fault can be expressed as:

$$I_{arm, \max} = I_{dc}/3 + I_m/2 + \Delta I_{dc}/3$$

(A3)

where the positive direction of  $I_{dc}$  is the direction that flows out from DC terminal; and  $I_m$  is the amplitude of AC current, satisfying  $0.75mI_m\cos\theta=I_{dc}$ , m and  $\theta$  are the modulation indexes and power factor angle, respectively. In order to maintain the continuous operation of MMC,  $I_{arm}$  is generally limited to 2 p.u. during Stage 1 [10]. Meanwhile, if the circulated current injection control is considered [25], the limitation will be stricter. Therefore, in this paper, a limitation of 1.70 p.u. is adopted. Assuming m=0.9,  $\cos\theta=1$ , the current increment can be estimated as:

$$\Delta I_{dc} \le 0.7 I_{dc} + 1.4 I_{dc} / (m \cos \theta) \approx 2.26 I_{dc}$$

(A4)

Substituting (A1) and (A4) into (A2), we can obtain:

$$\Delta V_{dc} \le 0.06 V_{dc} \tag{A5}$$

### 2) Inverter Operation Mode

Similarly, the maximum arm current of MMC during the fault is expressed as:

$$I_{arm, \max} = -I_{dc}/3 + I_m/2 + \Delta I_{dc}/3$$

(A6)

Substitute the limitation of 1.7 p.u. into (A6), it yields:

$$\Delta I_{dc} \le 2.7 I_{dc} + 1.4 I_{dc} / (m \cos \theta) \approx 4.26 I_{dc}$$

(A7)

Thus, the maximum voltage variation can be obtained:

$$\Delta V_{dc} \le 0.1 V_{dc} \tag{A8}$$

Combining (A5) and (A8), it is concluded that the voltage variation of DC equivalent capacitor during Stage 1 is within 0.1 p.u..

#### APPENDIX B

TABLE BI

PARAMETERS OF DETAIL SWITCHING MODEL AND AVERAGE-VALUE MODEL

| Parameter                   | Value |

|-----------------------------|-------|

| Rated DC voltage (kV)       | 500   |

| Rated AC voltage (kV)       | 260   |

| Rated DC current (kA)       | 1.5   |

| Arm inductance (mH)         | 100   |

| Arm resistance $(\Omega)$   | 1.32  |

| Sub-module capacitance (mF) | 1     |

| Number of sub-modules       | 20    |

Fig. B1. Configuration of average-value model based MMC.

## REFERENCES

- [1] Y. Chang, J. Hu, and X. Yuan, "Mechanism analysis of DFIG-based wind turbine's fault current during LVRT with equivalent inductances," *IEEE Journal of Emerging and Selected Topics in Power Electron*ics, Nov. 2019, doi: 10.1109/JESTPE.2019.2956085

- [2] CIGRE Working Group. HVDC grid feasibility study. Apr. 2013.

- [3] M. Xiang, J. Hu, and Y. Qiu, "Coordinated control of power loss and capacitor voltage ripple reduction for AC voltage boosted FBSM MMC with second harmonic circulating current injection," *High Volt*age, vol. 3, no. 4, pp. 272-278, Dec. 2018.

- [4] X. Pei, G. Tang, and S. Zhang, "Sequential auto-reclosing strategy for hybrid HVDC breakers in VSC-based DC grids," *Journal of Modern Power Systems and Clean Energy*, vol. 7, no. 3, pp. 633-643, May 2019.

- [5] W. Leterme, P. Tielens, S. D. Boeck et al., "Overview of grounding and configuration options for meshed HVDC grids," *IEEE Transac*tions on Power Delivery, vol. 29, no. 6, pp. 2467-2475, Dec. 2014.

- [6] J. Qin, M. Saeedifard, A. Rockhill et al., "Hybrid design of modular multilevel converters for HVDC systems based on various submodule circuits," *IEEE Transactions on Power Delivery*, vol. 30, no. 1, pp. 385-394, Feb. 2015.

- [7] R. Zeng, L. Xu, L. Yao et al., "Pre-charging and DC fault ridethrough of hybrid MMC based HVDC systems," *IEEE Transactions* on Power Delivery, vol. 30, no. 3, pp. 1298-1306, Jun. 2015.

- [8] L. Lin, Z. He, J. Hu et al., "Pole-to-ground fault ride through strategy for half-/full-bridge hybrid MMC based radial multi-terminal HVDC systems with low-impedance grounded," *IET Generation*, *Transmis-sion & Distribution*, vol. 12, no. 4, pp. 1038-1044, Feb. 2018.

- [9] M. Callavik, A. Blomberg, J. Häfner et al., "The hybrid HVDC breaker-aninnovation breakthrough enabling reliable HVDC grids," ABB Grid Systems, Technical Paper, Nov. 2012.

- [10] R. Li, L. Xu, D. Holliday et al., "Continuous operation of radial multiterminal HVDC systems under DC fault," *IEEE Transactions on Pow*er Delivery, vol. 31, no. 1, pp. 351-361, Feb. 2016.

- [11] Math Works. Sim Power Systems User, Natick, MA: The Math Works, 2014.

- [12] CIGRE Working Group. Guide for the development of models for HVDC converters in a HVDC grid. Dec. 2014.

- [13] E. D. Kimbark, "Transient overvoltages caused by monopolar ground fault on bipolar DC line: theory and simulation," *IEEE Transactions* on *Power Apparatus Systems*, vol. 89, no. 4, pp. 584-592, Apr. 1970.

- [14] Y. Zhang, N. Tai, and B. Xu, "Fault analysis and traveling-wave protection scheme for bipolar HVDC lines," *IEEE Transactions on Power Delivery*, vol. 27, no. 3, pp. 1583-1591, Jul. 2012.

- [15] X. Chu, G. Song, and J. Liang, "Analytical method of fault characteristic and non-unit protection for HVDC transmission lines," CSEE Journal of Power and Energy Systems, vol. 2, no. 4, pp. 37-43, Dec. 2016.

- [16] J. Beerten, S. D. Arco, and J. A. Suul, "Frequency-dependent cable modeling for small-signal stability analysis of VSC-HVDC systems," *IET Generation, Transmission & Distribution*, vol. 10, no. 6, pp. 1370-1381, 2016.

- [17] J. Yang, J. E. Fletcher, and J. O'Reilly, "Short-circuit and ground fault analyses and location in VSC-based DC network cables," *IEEE Trans*actions on *Industrial Electronics*, vol. 59, no. 10, pp. 3827-3837, Oct. 2015.

- [18] N. Yousefpoor, A. Narwal, and S. Bhattacharya, "Control of DC-fault resilient voltage source converter-based hvdc transmission system under dc fault operating condition," *IEEE Transactions on Industrial Electronics*, vol. 62, no. 6, pp. 3683-3690, Jun. 2015.

[19] C. Li, C. Zhao, J. Xu et al., "A pole-to-pole short circuit fault current

- [19] C. Li, C. Zhao, J. Xu et al., "A pole-to-pole short circuit fault current calculation method for DC grids," *IEEE Transactions on Power Sys*tems, vol. 32, no. 6, pp. 4943-4953, Nov. 2017.

- [20] J. Dai, J. Qiu, J. Wu et al., "Research on power flow calculation method of multi terminal hybrid DC grid based on multiple control modes," in *Proceedings of IEEE ICPES*, Colombo, Sri Lanka, Dec. 2018, pp. 1-6.

- [21] R. Zeng, L. Xu, and L. Yao, "DC/DC converters based on hybrid MMC for HVDC grid interconnection," in *Proceedings of IET ACDC Conference*, Birmingham, U.K., Jan. 2015, pp. 1-6.

- [22] J. Suonan, S. Gao, G. Song et al., "A novel fault-location method for HVDC transmission lines," *IEEE Transactions on Power Delivery*, vol. 25, no. 2, pp. 1203-1209, Apr. 2010.

- [23] W. Wang, M. Barnes, O. Marjanovic et al., "Impact of DC breaker systems on multiterminal VSC-HVDC stability," *IEEE Transactions* on *Power Delivery*, vol. 31, no. 2, pp. 769-779, Apr. 2016.

- [24] C. Li, L. Lin, Z. He *et al.*, "Optimized design of DC-side smoothing reactors in meshed multi-terminal HVDC systems based on symmetrical bipolar modular multilevel converter," *Journal of Engineering*, vol. 2017, no. 13, pp. 1225-1231, 2017.

- [25] M. Lu, J. Hu, R. Zeng et al., "Imbalance mechanism and balanced control of capacitor voltage for a hybrid modular multilevel converter," *IEEE Transactions on Power Electronics*, vol. 33, no. 7, pp. 5686-5696, Aug. 2018.

Zhen He received the B.S. degree in electrical engineering from School of Electrical Engineering and Automation, Hefei University of Technology, He-

fei, China, in 2014. He is currently working toward the Ph. D. degree at State Key Laboratory of Advanced Electromagnetic Engineering and Technology, Huazhong University of Science and Technology, Wuhan, China. His current research interests include MMC for HVDC application and transient analysis technology of multi-terminal HVDC networks.

Jiabing Hu received the B. Eng. and Ph.D. degrees in the College of Electrical Engineering, Zhejiang University, Hangzhou, China, in 2004 and 2009, respectively. From 2007 to 2008, he was funded by Chinese Scholarship Council (CSC) as a visiting scholar with the Department of Electronic and Electrical Engineering, University of Strathclyde, Glasgow, U.K. From April 2010 to August 2011, he was a Post-Doctoral Research Associate with Sheffield Siemens Wind Power (S2WP) Research Center and the Department of Electronic and Electrical Engineering, University of Sheffield, Sheffield, U.K. Since September 2011, he has been a professor with State Key Laboratory of Advanced Electromagnetic Engineering and Technology, and School of Electrical and Electronic Engineering, Huazhong University of Science and Technology, Wuhan, China. His current research interests include grid-integration of large-scale renewables, and modeling, analysis and control of power electronized power systems.

Lei Lin received the B.S., M.S., and Ph.D. degrees in electrical engineering from the School of Electrical and Electronic Engineering, Huazhong University of Science and Technology, Wuhan, China, in 2001, 2004, and 2007, respectively. He has been engaged in the teaching and research in the field of power electronics from 2007 in School of Electrical and Electronic Engineering, Huazhong University of Science and Technology, Wuhan, China. From 2007 to 2009, he was a Postdoctoral Fellow. From 2009 to 2010, he was a Lecturer. And since 2010, he has been an Associate Professor with State Key Laboratory of Advanced Electronagnetic Engineering and Technology, and School of Electrical and Electronic Engineering, Huazhong University of Science and Technology, Wuhan, China. His current research interests include MMC for HVDC applications, high-voltage capacitor charging power supply, multilevel converters, and related control techniques.

Yuanzhu Chang received the B.Eng. degree from the School of Electrical and Electronic Engineering, Huazhong University of Science and Technology, Wuhan, China, in July 2014. He is currently working toward the Ph.D. degree with the State Key Laboratory of Advanced Electromagnetic and Technology, School of Electrical and Electronic Engineering, Huazhong University of Science and Technology. His current research interests include fault analysis and protection of power electronized power systems.

Zhiyuan He received the B.Eng. degree from Sichuan University, Chengdu, China, in 2000, and the M.Eng. and Ph.D. degrees from China Electric Power Research Institute (CEPRI), Beijing, China, in 2003 and 2006, respectively. In 2006, he joined CEPRI, where he led the voltage source converter (VSC)-HVDC Transmission Systems Group. In the past six years, he has accomplished the study on high-power electronics technology for reliable operation of large interconnected power grids. Dr. He was a member of CIGRE B4 Working Group 48. His research interests include VSC-HVDC control and testing technologies.